## DESIGN AND IMPLEMENTATION OF AN PID CONTROLLED EFFICIENT BUCK-BOOST CONVERTER USING INTERLEAVED TOPOLOGY

Santhanagopalan.A, Final year EEE, Saranathan College of Engg, Venkateswara Nagar, Trichy – 12. santoap93@gmail.com

Abstract—A DC-DC converter is of great importance in the converter is improved than the conventional field of sustainable energy. This paper deals with the Buckuck-boost converters.

Boost converter which converts a DC voltage to a higher value (step up) and also to a lower value (step down). But due to various switching losses, conduction losses across the passive elements, there is a reduction in efficiency which deteriorates the converter performance. Thus to avoid a Interleaved topology is employed. Where two buck-boost converters operate in parallel and reduce the switching stress and reduce the ripple content of the input current as the switches operate 180° out of phase. Thus this paper analyses the efficiency and the output values of both Buck-Boost and Interleaved Buck-Boost converter and the results are simulated with the help of MATLAB / SIMULINK environment.

Keywords: Buck-Boost converter; Interleaved Buck-Boost converter; Efficiency; Ripple cancellation.

#### 1. INTRODUCTION

A suitable DC-DC converter is required for designing high efficiency power systems. Among the various topologies, Interleaved buck-boost converter is considered as a better solution for high power systems due to improved electrical performance, reduced weight and size. Detailed analysis has been done to investigate the benefits of interleaved buck-boost converter compared to the conventional buck-boost converter topologies.

Due to the current handling limitation of single switch, the output power is small, typically tens of watts. At a higher current, the size of these components increases, with increased component losses, and the efficiency decreases. The simplest way of describing a interleaved converter is to see it as consisting of several power stages (converter "phases") with inputs parallel and drive signals shifted to ensure uniform distribution over a switching period.

In pratical case there will be formation of harmonics and current ripples and voltage losses along the passive elements of the power converter. Hence the pratical values will be lesser than the calculated one. These losses can be reduced by using interleaved topology. Where the gate pulses to the transistors in parallel with the inductors are 180° out of phase with each other with the same frequency thus the ripples in the input inductor current will get reduced. And thus the efficiency of

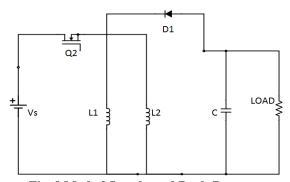

#### 2. BUCK-BOOST CONVERTER

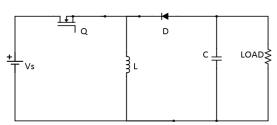

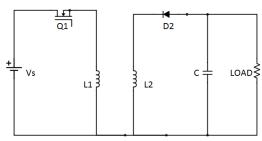

Fig. 1 Schematic diagram of Buck-Boost Converter

Buck-Boost converter belongs to the family of basic power conversion topologies (the other two being buck and buck-boost derivative). The schematic diagram of buck-boost converter is shown in Fig. 1. Buck-Boost converters are probably the most versatile paths to sustainable energy power converters today. It is typically used when output voltage can be made either higher or lower than the input voltage. It uses only one switch, employing only one stage conversion, and requires inductors and capacitors for energy transfer. It provides output voltage of reverse polarity. Hence care must be taken by switching the terminals while using the converted power for practical applications.

The relationship between the input voltage and the output voltage is

$$V_o = \frac{-V_s d}{1 - d} \tag{1}$$

Where  $d = \frac{T_{on}}{T}$  is the duty cycle ratio.  $T_{on}$  is the ON time of the semiconductor switch and T is the switching period. In continuous current mode of conduction the selected value of inductance should be greater than the critical value of the inductance  $L_c$ . The value of inductance L and capacitance C can be found by [1]:

$$\Delta I = \frac{V_s d}{fL} \tag{2}$$

$$\Delta V_c = \frac{I_o d}{fc} \tag{3}$$

Where  $\Delta I$  is the ripple current,  $\Delta V_c$  is the ripple voltage, f is the switching frequency, L is the filter inductance and C is the filter capacitance of the circuit.

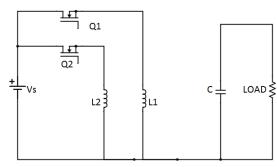

### 3. INTERLEAVED BUCK-BOOST CONVERTER

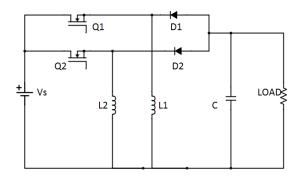

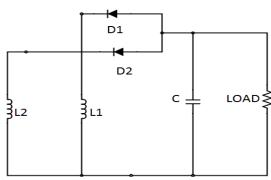

Fig. 2 Schematic diagram of Interleaved Buck-Boost Converter

Due to the current handling limitation of single switch, the output power is small, typically tens of watts. At a higher current, the size of these components increases, with increased component losses, and the efficiency decreases. The simplest way of describing a Interleaved converter is to see it as consisting of several power stages (converter "phases") with inputs and outputs connected in parallel and drive signals shifted to ensure uniform distribution over a switching period .

#### 4. DESIGN CONSIDERATIONS

For designing the interleaved buck-boost power converter we must choose the appriopriate value for the inductor and capacitive filter used whose value is given by,

$$L1 = L2 = \frac{vsd}{f\Delta I} \tag{4}$$

$$C = \frac{Iad}{f\Delta Vc} \tag{5}$$

Table 1. Design parameters of Interleaved Buck-Boost Converter

| Parameter                        | Values |

|----------------------------------|--------|

| Input voltage(V)                 | 10 V   |

| Output voltage(V₀)               | 15 V   |

| Output power(P <sub>0</sub> )    | 25 W   |

| Ripple voltage (Δ <sub>V</sub> ) | 0.017  |

| Ripple current( $\Delta I_1$ )   | 4.645  |

| Inductor (L1= L2)                | 52µH   |

| Output capacitance               | 2.5 mF |

| Resistance(R <sub>0</sub> )      | 9 Ώ    |

| Duty ratio (d)                   | 60 %   |

In pratical case there will be formation of harmonics and current ripples and voltage losses along the passive elements of the power converter. Hence the pratical values will be lesser than the calculated one. These losses can be reduced by using interleaved topology. The inductor and capacitor values of the interleaved buck-boost converter is derived from equation (2) and (3).

## 4. SIMULATION RESULTS AND DISCUSSION

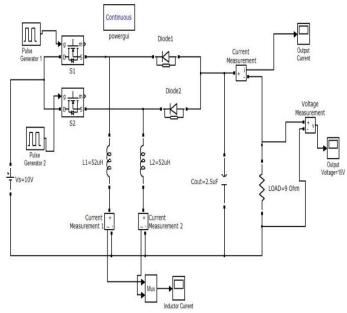

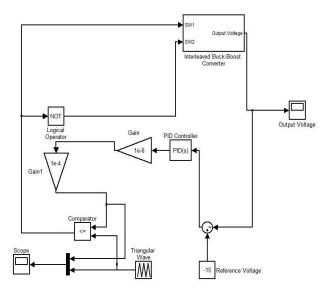

Fig. 3. MatLAB / Simulink diagram of Buck-Boost converter

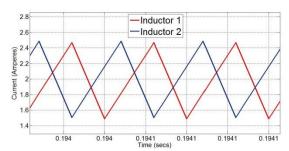

The proposed interleaved buck-boost converter is simulated using MATLAB / SIMULINK is shown in Fig. 3. The ultimate aim is to achieve a ripple free high efficiency buck-boost converter operation. Where the gate pulses to the transistors in parallel are 180° out of phase with each other with the same frequency thus the ripples in the input inductor current will get reduced. The interleaved buck-boost converter is designed using Table II. The designed DC-DC converter simulated using Matlab is depicted in Fig. 3. Input inductor current L1 and L2 are given in Fig. 4. The MOSFETs are operated by 180° out of phase, the ripple present in the current are eliminated. The current from the inductors are out of phase with each other, hence 3<sup>rd</sup> order harmonics present in the current is eliminated. Hence the small value of capacitor is enough to eliminate the rest of the harmonics present in the load current.

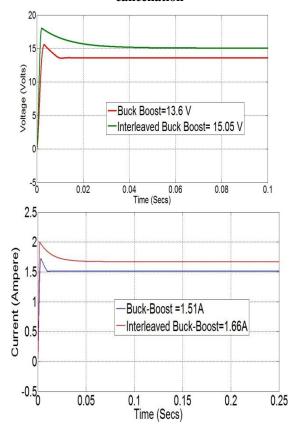

The output voltage response of the buck-boost converter and interleaved buck-boost converter are given in Fig. 5. Both the circuits are simulated with the input voltage of 10 V and the duty cycle of the pulse given to the switches is 60 %. The obtained output voltage of the buck-boost converter is only 13.6 V, but the output voltage of the interleaved buck-boost converter is 15.05 V. Similarly the Output Current for the Buck-Boost converter is only 1.51A but it is 1.66 A in the case of an

Interleaved Buck Boost converter, which shows that there is an improved efficiency.

Fig. 4 Input Inductive current ripple cancellation

Fig. 5. Output Voltage and Output current of the Buck-Boost and Interleaved Buck-Boost Converter

Both the converter output consists of peak overshoot. This ripple cancellation helps to reduce the voltage drop and increase the output voltages in the conventional and interleaved Buck-Boost converter.

#### 5. EFFICIENCY ANALYSIS

The efficiency calculation of the Buck-Boost and the interleaved Buck-Boost converter are given below: The equations corresponding to the calculations are,

$$Efficiency = \frac{Pout}{(Pout+Ps+Pl+Pd)}$$

(6)

The conduction loss  $(P_{SC})$  and switching loss  $(P_{ss})$  of the MOSFET are

$$P_{SC} = Rs \times d \times (Ia/1 - d)^{2}$$

(7)

$$P_{ss} = \frac{1}{2} f s V_s I_L \left( t_{on} + t_{off} \right) \tag{8}$$

$$PS = P_{SC} + P_{sd} \tag{9}$$

Where, Rs is MOSFET ON resistance,  $t_{on}$  is the ON time of the switch,  $t_{off}$  is the OFF time of the switch, d is the duty ratio, and  $I_L$  is the current through an inductor.

The conduction loss in the inductor (Pl)

$$PI = RL \times (Ia/1 - \delta)^2$$

(10)

The conduction loss (Pd) and switching loss ( $P_{sd}$ ) of the diode

$$Pcd = R_D \times Ia^2 + VF \times Ia$$

(11)

$$P_{sd} = \frac{1}{2} f s V_s I_L (t_{on} + t_{off})$$

(12)

$$Pd = Pcd + P_{sd} (13)$$

Where, VF is the forward ON Voltage,  $R_D$  is the Diode resistance, and Ia is the output current. Thus the input power

$$P_{IN} = Pout + Ps + Pl + Pd$$

(14)

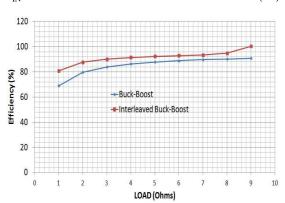

Fig. 6 Efficiency graph for buck-boost and interleaved buck-boost converter

Efficiency graph buck-boost for interleaved buck-boost converter is portrayed in Fig. 10. The efficiency of both the converters are calculated using the equation (14) to (22). The load resistance is varied from 1 Ohm to 9 Ohm; the corresponding efficiency values are plotted. For every load resistance value efficiency of the interleaved buck-boost converter is higher than the conventional buck-boost converter. Thus it is evident from the above graph that the interleaving technique improves the efficiency of the Buck-Boost converter by 2% to 6%. As it reduces the ripple and reduces the heat dissipation of the inductor used.

# .6. DESIGNING OF CLOSED LOOP PID CONTROLLER FOR INTERLEAVED BUCK-BOOST CONVERTER

For designing the closed loop PID controller for the converter state space modelling is done to determine the transfer function of the system and then by using Ziger Nicholas chart and Routh stability criterion the values proportional, Integral and Differential gains are determined and the stability of the controller is determined through MATLAB programs from which the closed loop is simulated by SIMULINK.

#### 5.1 .State Space Modelling

There are four modes of operation for an interleaved buck-boost converter based on the ON/OFF state of the switches. Since this design deals only with two switches there are four states of operation which are tabulated below

Table 2. Modes Of Operation Of Interleaved Buck-Boost Converter

| Mode | Q1  | Q2  |

|------|-----|-----|

| 1    | ON  | ON  |

| 2    | OFF | ON  |

| 3    | ON  | OFF |

| 4    | OFF | OFF |

#### 5.1.1 .Mode 1: Q1 and Q2 ON

In mode 1 operation, both transistors Q1 and Q2 are ON and diodes D1 and D2 are reverse biased. The inductor stores the supplied energy  $(1/2 \text{ LI}^2)$ .

Fig. 7 Mode 1 Interleaved Buck-Boost Converter

The governing equations of mode 1 is expressed as

$$\frac{di_{L1}}{dt} = \frac{V_S}{L1} \tag{15}$$

$$\frac{di_{L2}}{dt} = \frac{V_S}{L2} \tag{16}$$

$$\frac{dV_0}{dt} = \frac{V_0}{RC} \tag{17}$$

The state space parameters for mode 1 are given by,

$$A1 = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 0 & 0 \\ 0 & 0 & \frac{-1}{RC} \end{bmatrix} \tag{18}$$

$$B1 = \begin{bmatrix} \frac{1}{L1} \\ \frac{1}{L2} \\ 0 \end{bmatrix} \tag{19}$$

#### 5.1.2.Mode 2: Q1 OFF, and Q2 ON

Fig. 8 Mode 2 Interleaved Buck-Boost Converter

In mode 2 the transistor Q1 is OFF and Q2 is ON and the diode D1 is forward biased and D2 is reversed biased. Thus L1 discharges to the capacitor C1.The governing equations of mode 2 can be described by:

$$\frac{di_{L1}}{dt} = \frac{V_0}{L1} \tag{19}$$

$$\frac{di_{L2}}{dt} = \frac{V_S}{L2} \tag{20}$$

$$\frac{dV_0}{dt} = \frac{i_{L1}}{c} - \frac{V_0}{RC}$$

(21)

The state space parameters for mode 2 are given by,

$$A2 = \begin{bmatrix} 0 & 0 & \frac{1}{L1} \\ 0 & 0 & 0 \\ \frac{-1}{c} & 0 & \frac{-1}{RC} \end{bmatrix}$$

(22)

$$B2 = \begin{bmatrix} \frac{1}{L1} \\ 0 \\ 0 \end{bmatrix}$$

(23)

#### 5.1.3 Mode 3: Q1 ON, and Q2 OFF

Fig. 9 Mode 3 Interleaved Buck-Boost Converter

In the mode 3 operation, the transistors Q1 ON and Q2 OFF and diode D1 reverse biased and D2 forward biased. Thus L2 discharges to the capacitor C1 The equivalent circuit equations are derived as

$$\frac{di_{L1}}{dt} = \frac{V_s}{L1} \tag{24}$$

$$\frac{di_{L2}}{dt} = \frac{V_s}{L2} \tag{25}$$

$$\frac{dV_o}{dt} = \frac{i_{L2}}{C} - \frac{V_o}{RC} \tag{26}$$

The state space parameters for mode 3 are given by,

$$A3 = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 0 & \frac{1}{L^2} \\ 0 & \frac{-1}{C} & \frac{-1}{RC} \end{bmatrix}$$

(27)

$$B3 = \begin{bmatrix} 0 \\ \frac{1}{L2} \\ 0 \end{bmatrix} \tag{28}$$

Fig. 10 Mode 4 Interleaved Buck-Boost Converter

Finally, during the Mode 4 operation, the transistors Q1 and Q2are OFF and the diodes D1 and D2 are forward biased Thus both the inductors L1 and L2 discharges to the capacitor C1. The equations of mode 4 are

$$\frac{di_{L1}}{dt} = \frac{V_0}{L1} \tag{29}$$

$$\frac{di_{L2}}{dt} = \frac{V_0}{L2} \tag{30}$$

$$\frac{dV_0}{dt} = \frac{i_{L1}}{c} + \frac{i_{L2}}{c} - \frac{V_0}{RC}$$

(31)

The state space parameters for mode 4 are given by,

$$A4 = \begin{bmatrix} 0 & 0 & \frac{1}{L1} \\ 0 & 0 & \frac{1}{L2} \\ \frac{-1}{C} & \frac{-1}{C} & \frac{-1}{RC} \end{bmatrix}$$

(32)

$$B4 = \begin{bmatrix} \frac{d1+d2}{L1} \\ \frac{d1+d3}{L2} \\ 0 \end{bmatrix}$$

(33)

Thus the state space equation for the entire system is given by,

$$A=A1*d1+A2*d2+A3*d3+A4*d4$$

(34) Therefore,

#### 5.1.4.MODE 4: Q1 OFF and Q2 OFF

$$A = \begin{bmatrix} 0 & 0 & \frac{d3+d4}{L1} \\ 0 & 0 & \frac{d2+d4}{L2} \\ \frac{-(d3+d4)}{C} & \frac{-(d2+d4)}{C} & \frac{-1}{RC} \end{bmatrix} (35)$$

Similarly,

$$B = B1*d1 + B2*d2 + B3*d3 + B4*d4$$

(35)

$$B = \begin{bmatrix} \frac{d1+d2}{L1} \\ \frac{d1+d3}{L2} \\ 0 \end{bmatrix}$$

(36)

And, As the controller is based on output voltage sensing,

C=[001]; D=[0]

Thus the state space model is given by,

X'=AX+BU; and Y=CX'+DU. Where,

$$X = \begin{bmatrix} i_{L1} \\ i_{L2} \\ V_o \end{bmatrix} \tag{37}$$

$$X' = \frac{dX}{dt} = \begin{bmatrix} i'_{L1} \\ i'_{L2} \\ V'_{Q} \end{bmatrix}$$

(38)

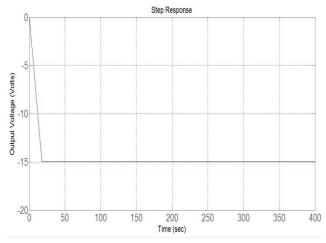

Fig 11. step response of the transfer function

Thus from the derived state space model we can get the transfer function and its response given by,

The step response of the transfer function is given below. The Characteristics equation is given by,

$$1+G(s).H(s) = 0$$

(40)

Now, by using Routh stability criterion and Ziger Nicolas chart the values of proportional, Integral and Differential gains are determined which are given by,

$$K_p=1$$

;  $K_i=7e10$ ;  $K_d=1e6$

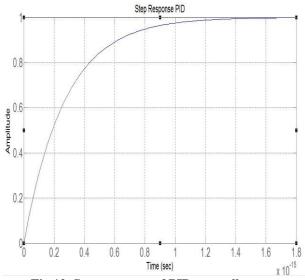

Fig 12. Step response of PID controller

Thus from the above response the system seems to be stable at an settling time of 1.6 feta secs.

#### 7. SIMULATION AND RESULTS OF CLOSED LOOP PID CONTROLLED INTERLEAVED BUCK-BOOST CONVERTER

The calculated values are simulated using SIMULINK and the result are shown,

Fig 13. SIMULINK diagram of PID Controller

The above figure shows the SIMULINK diagram of PID closed loop simulation the results of the simulations are shown below.

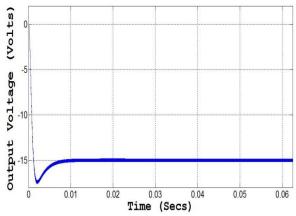

Fig 14. Output Boost Configuration

The above figure shows the output when the reference is 15V which is the boost configuration.

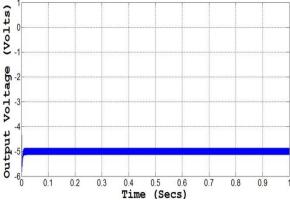

Fig 15. Output Buck Configuration

The above figure shows the output when the reference is 5V which is the buck configuration.

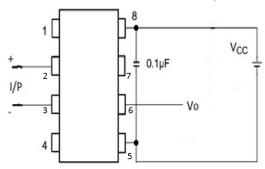

#### 7. .HARDWARE IMPLEMENTATION

This project deals with the Open loop Configuration of Interleaved Buck-Boost Converter alone for hardware implementation. For the hardware the converter prototype is designed for 1Watt.The corresponding PCB (Printed Circuit Board) are fabricated which involves the following components

- 1.Mosfet-2 Pieces-IRF840

- 2.Inductor 1.5H -2 Pieces

- 3. Capacitor 10µF -1 Piece

- 4. Mosfet Driver IC-TLP250- 2 Pieces

5.

The Mosfet Driver is used to amplify the gate pulse voltage to the Mosfet threshold needs by push pull amplification.

The schematic of TLP250is shown below,

Fig 16. Schematic of TLP250 Mosfet driver

It should be noted that the Vcc bust be between 12V to 20V which is the operating range of the driver. A capacitor is connected across the supply pins to filter the ripples in the supply. Pins 2 and 3 forms the input and Pin 6 is the output pin which is connected to the gate of the mosfet. The hardware is implemented and the results are shown below.

Fig 17. Boost operation 60% duty cycle

Fig 18. Buck operation 40% duty cycle

#### REFERENCES

- [1] D.Lakshmi M.Tech, S.Zabiullah M.Tech, Dr. Venu gopal.N M.E,PhD., Improved Step down Conversion in Interleaved Buck Converter and Low Switching Losses, Research Inventy: International Journal Of Engineering And Science Vol.4. Issue 3(March 2014). PP 15-24

- [2] Farag. S. Alargt "Analysis and Simulation of Interleaved Boost Converter for Automotive Applications International Journal of Engineering and Innovative Technology (IJEIT) Volume 2, Issue 11, May 2013

- [3] Il-Oun Lee, Student Member, IEEE, Shin-Young Cho, Student Member, IEEE, and Gun-Woo Moon, Member, IEEE, Interleaved Buck Converter Having Low Switching Losses and Improved Step-Down Conversion Ratio, IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 27, NO. 8, AUGUST 2012.

- [4] Interleaved Buck Converter using Low Voltage and High Current Application, International Journal of Applied Engineering Research, ISSN 0973-4562, Vol. 8, No. 19 (2013).

- [5] M.H. Rashid, 'Power Electronics: Circuits, Devices and Applications', Pearson Education, PHI Third edition, NewDelhi 2004.

- [6] M.Shanmuga Priya, P.Parthasarathy, R.Saran RajPG Scholar, Department of EEE, Saranathan College of Engineering, Periyar Maniammai University, M.I.E.T College of Engineering, Trichy, India, Multi Device Interleaved Boost Converter for Water Pumping System, IJIRSET.

- [7] M. Vellaiyaras, K. Esakki Shenbaga Logaand J. Jasper Gnana Chandran. Interleaved Buck-Boost Converter Fed DC Motor, International Journal of Electrical

- Engineering. ISSN 0974-2158 Volume 6, Number 3 (2013), pp. 301-309

- 8] Milan Ilic and Dragan Maksimovic, Senior Member, IEEE. ,Interleaved Zero-Current-Transition Buck Converter IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 43, NO. 6, NOVEMBER/DECEMBER 2007 1619

- [9] Suman Dwari, Student Member, IEEE, and Leila Parsa, Member, An Efficient High-Step-Up Interleaved DC–DC Converter With a Common Active ClampIEEE, IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 26, NO. 1, JANUARY 2011

- [10] Shenbaga Lakshmi, Sree Renga Raja, Observer-based controller for current mode control of an interleaved boostconverter by. Turk J Elec Eng & Comp Sci (2014) 22: 341-352

- [11] S. Sugumar, E.M. Saravanan, E. Dinesh, D. Elangovan and Dr. R. Saravanakumar.,Interleaved BuckConverter using Low Voltage and High Current Application, International Journal of Applied Engineering Research, ISSN 0973-4562, Vol. 8, No. 19 (2013)

- [12] Texas Instruments, An Interleaved PFC Preregulator for High-Power Converters

- [13] Vijayalakshmi, S and Sree Renga Raja T, Time Domain Based Digital Controller for Buck-Boost Converter by J Electr Eng Technol Vol. 9, No. 5: 1551 -1561, 2014.